Závislosť SOJ od inštrukčnej sady procesorov

Inštrukčné sady rôznych procesorov sa do veľkej miery líšia. Niektoré obsahujú

veľa zložitých inštrukcií, niektoré málo jednoduchých inštrukcií, niektoré využívajú

inštrukcie bez parametrov. Rozdielov je mnoho a výrazne ovlyvňujú aj zdrojové kódy

písané v SOJ a assembleroch.

Na čo slúžia inštrukcie?

Strojový jazyk pozostáva z diskrétnych inštrukcií. Pre architektúru, ktorá ich má vykonať môžu špecifikovať:

- registre pre aritmetické, adresné alebo ovládacie funkcie

- pamäťové miesta alebo offsety

- adresné módy, využívané k interprentácií operandov

Zložitejšie operácie vznikajú kombináciou týchto inštrukcií, ktoré sa vykonajú sekvenčne alebo na základe

riadiacej štruktúry.

Základné typy inštrukcií

Operácie, ktoré obsahuje väčšina procesorov:

Presuny

- Nastavenie registra na konštantnú hodnotu

- Presun hodnoty z určitého pamäťového miesta do registra alebo naopak

- načítanie alebo zápis údajov do hardvérových ovládačov

Výpočty

- Spočítanie, odčítanie, vydelenie, vynásobenie obsahov dvoch registrov a uloženie výsledku do registra

- Bitové operácie konjunkcia(and), diskunkcia(or), negácia(not)

- Porovnanie obsahov dvoch registrov (<,>,=)

Ovplyvňovanie behu programu

- Skok na určité návestie a vykonávanie programu od neho

- Skok na určité návestie, ak je splnená podmienka

- Skok na určité návestie, ale uloženie adresy nasledujúcej inštrukcie, aby bol možný návrat

RISC vs CISC

CISC charakteristika

Ešte na počiatku éry procesorov, neboli k dispozícií vyššie programovacie jazyky s kompilátormi a programy

boli písané výhradne v SOJ a prekladané assemblermi. A preto sa výrobcovia procesorov snažili vymyslieť také

inštrukcie, ktoré by vykonali čo najviac operácií naraz. Vtedy bolo zmýšľanie také, že hardvérový vývoj bol

jednoduchší ako softvérový vývoj kompliátorov. A preto miesto toho aby sa vymysleli softvéry, ktoré by dokázali

vykonať zložité inštrukcie, sa tieto zložité inštrukcie vložili priamo do inštrukčných sád procesorov. Hovoríme

o CISC procesoroch, v preklade o procesoroch so zložitou inštrukčnou sadou (complex instruction set computer).

CISC výhody

- uľahčenie písania kódov

- uľahčenie práce prekladačom

- kratšie a menšie kódy

- ortogonalita

- zložité dátové typy

Pôvodne bola táto inštrukčná sada vytvorená k zefektívneniu programovania. Mala uľahčiť prácu prekladačom aj programátorom.

Zložité inštrukcie s mnohými adresnými režimami mali umožniť programátorom programovať v SOJ podobne ako vo vyšších

programovacích jazykoch. Napríklad assembler procesoru Motorola 68000 je podobný dnešnému C. Prispieť k tomu mala

aj ortogonalita inštrukčnej sady, znamená to, že inštrukcie sa mohli používať v akýchkoľvek adresných módoch.

(Ortogonalita je vysvetlená nižšie). Okrem toho boli v hardvéri implementované zložité dátové typy a dalo sa pracovať

napríklad s komplexnými číslami, prípadne inštrukciami pre byteové reťazce.

CISC nevýhody

- stupňujúce sa nároky na hardvér(cenové, technické)

- nevyužívanie väčšiny zložitých inštrukcií

- pomalý beh programov

Tieto architektúry boli implementované prostredníctvom mikroprogramovania. Tým, že sa stále rozširovala inštrukčná

sada, sa zvyšovala aj zložitosť procesorov a tento trend nemohol pokračovať donekonečna.Typickými

predstaviteľmi CISC boli svojho času aj X86 Intel procesory(8086), ale neskôr museli zjednodušiť inštrukčnú

sadu. Okrem toho sa zistilo, že veľké množstvo zložitých inštrukcií v procesoroch sa vlastne vôbec ani nepoužívalo.

Dopad CISC na SOJ

Aby som demonštroval zložitosť inštrukčnej sady CISC procesorov, uvediem krátky

zdrojový kód.

Všimnite si:

- rôznych adresných režimov

- implicitne zadaných operandov u inštrukcie imul

- segmentového adresovanie pomocou segmentového registra es

- u aritmetických inštrukcií je možné používať operandy priamo načítané z operačnej pamäte (mov es: [di], ax, add ax, [ zy1])

Toto všetko je pre CISCové architektúry typické a naopak netypické pre architektúru RISC

V skratke môžeme povedať, že zdrojové kódy písané pre CISC architektúry sú kratšie, pretože sa minimalizuje

počet inštrukcií v programe, má to ale svoj dopad na efektivitu, pretože každá zložitá inštrukcia sa musela vykonať

v 100-300 taktoch.

RISC - jednoduchosť a rýchlosť

S príchodom vyšších programovacích jazykov sa prišlo na myšlienku(IBM 1980), že by sa dal dosahovať vyšší výkon

s použitím jednoduchých inštrukcií, ktoré by sa ale vykonávali rýchlo. Takto vznikli architektúry s redukovanou

inštrukčnou sadou (reduced instruction set computer) RISC. Avšak nakoniec sa ukázalo, že sa využívalo len 30%

všetkých možných kombinácií inštrukcií. To znamená, že investícia do zložitého

CISC mikroprocesora bola vlastne v tom prípade zbytočná, pretože jeho veľká časť zostala nevyužitá.

Základné vlastnosti:

- dôraz na softvér

- jednoduché inštrukcie, vykonajú sa v jednom takte

- jednotný formát inštrukcií (ľahšie dekódovanie)

- identické registre pre všeobecné použitie

- jednoduché adresné módy

- dlhšie a väčšie kódy

- menej dátových typov priamo v hardvéri

- obmedzenie ortogonality

- velké množstvo registrov

Výhody RISC architektúry

- menšia hardvérová zložitosť

- rýchlejší beh programov

- univerzálne použiteľné všeobecné registre

Od 80tych rokov začalo platiť, že procesory sa stali rýchlejšie ako k nim prislúchajúce pamäte. Tento rozdiel

sa postupne stále prehlbuje a práve to sa najviac využíva v RISC architektúrach. Reakciou na to bolo zavedenie

veľkého množstva pracovných registrov, pričom mohlo byť zväčšené pomocou registrového okna, kde sa dalo prepínať

medzi viacerými sadami registrov. Pracovné registre sú cache pamäť nultej úrovne, prístup do nich je veľmi rýchly.

Dôležité je, že všetky registre sú rovnocenné, žiadny nemá funkciu akumulátora, čo uľahčuje prácu programátorom v SOJ

aj prekladačom.

Nevýhody RISC

- zložitejšie kódy

- väčšie kódy

Samozrejme tým, že inštukčné sady neobsahujú rôzne zložité inštrukcie je na programátorovi aby si ich nahradil

vhodnou postupnosťou jednoduchých inštrukcií. Kódy sa samozrejme stávajú dlhšími, ale tento nedostatok RISC architktúry

sa eliminuje v súčasnosti tým, že vznikajú hybridné RISC a CISC procesory.

Dopad RISC na SOJ

Už som spomenul všetko, v tejto časti to len zosumarizujem.

- zložitejšie kódy

- univerzálne využitie pracovných registrov

- väčší počet registrov

- rýchlejší beh programov

Súčasné procesory - RISC či CISC ?

Súčasný trend sa uberá takým smerom, že vznikajú určité hybridy medzi RISC a CISC procesormi. Keďže sú však

veľmi rýchle väčšinou sú nazývanými RISC procesormi. V minulosti sa zdalo, že CISC architektúra bude úplne nahradená.

Ale ona mala svoje výhody a v súčasnosti sa efektívne využívajú. Súčasné procesory sa vyznačujú týmito vlastnosťami:

- velká rýchlosť a interná jednoduchosť ako v RISC

- kratšie kódy inštrukcií ako v CISC(menšie nároky na vyrovnávaciu pamäť)

Do tejto fázy dospeli aj X86 procesory prípadne aj Motorola procesory(M68060), ktoré boli pred tým CISC architektúrami.

Docieľuje sa to tým, že inštrukčné sady sú o trochu rozšírené oproti RISC procesorom, ale zároveň sa zachováva

vysoké množstvo registrov a tým pádom aj rýchlosť a okrem toho sa zlepšuje aj prehľadnosť kódov v SOJ.

Rozdelenie

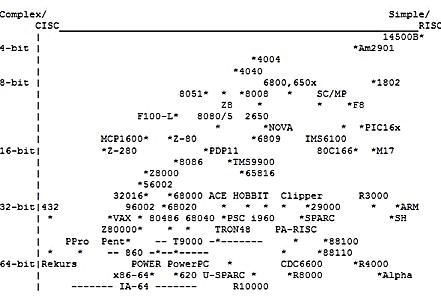

Je veľmi ťažké presne zaradiť procesory k RISC alebo CISC architektúre. Nasledujú obrázok ukazuje, kde sa asi

nachádzajú jednotlivé procesory vzhľadom na zložitosť inštukčnej sady.

Obr.1 RISC a CISC procesory

Zásobníkové procesory

Jedná sa o architektúru, ktorá priamo vo svojich inštrukciách podporuje prácu so zásobnikom

a dokonca môže vo svojom jadre obsahovať 1 alebo viac zásobníkov. Nejedná sa ale o

základnú manipuláciu so zásobnikom, to zvládajú všetky procesory, ide skôr o pokročilé operácie nad zásobníkom ako

inštrukcie OVER(skopíruje druhú položku od vrchola zásobíka), DUP(skopíruje vrchnú položku zásobníka).

Využitie zásobníkových procesorov

Zásobníkové procesory sa kombinujú niekedy napríklad s RISC procesormi.

Využitie nájdu:

- pri písaní programov pre vnorené systémy

- v družiciach pri riadiacih a meracích činnostiach

- v systémoch vyžadujúcich vysokú rýchlosť spracovania a rýchle odozvy na prerušenia(

nie je potrebné uložit stav procesoru pri prerušení, lebo všetko podstatné je už v zásobniku)

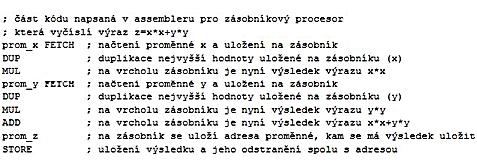

Zásobníkové procesory a ich dopad na SOJ

- kratšie kódy ako pri RISC a CISC

- neobsahuje registre ani plánovač inštrukcií

- inštrukcie bez explicitného adresovania(okrem LOAD,STORE)

Obr.2 Ukážka kódu v SOJ pre zásobníkovú architektúru